# **USER MANUAL AGILENT ACQIRIS SIGNAL ANALYZERS** INCLUDING

**BASE TEST**

AND

**FFT SPECTROMETER FIRMWARE**

Models covered: AC210 U1091AAC1 AC240 U1080A-001

**Agilent Technologies**

#### **Manual Part Number**

## U1092-90006

#### **Edition**

A-Revl, February 2009

The information in this document is subject to change without notice and may not be construed in any way as a commitment by Agilent Technologies Inc. While Agilent Technologies makes every effort to ensure the accuracy and contents of the document it assumes no responsibility for any errors that may appear.

The information in this document is subject to change without notice and may not be construed in any way as a commitment by Agilent Technologies, Inc. While Agilent makes every effort to ensure the accuracy and contents of the document it assumes no responsibility for any errors that may appear.

All software described in the document is furnished under license. The software may only be used and copied in accordance with the terms of license. Instrumentation firmware is thoroughly tested and thought to be functional but it is supplied "as is" with no warranty for specified performance. No responsibility is assumed for the use or the reliability of software, firmware or any equipment that is not supplied by Agilent or its affiliated companies.

You can download the latest version of this manual from http://www.agilent.com/ by clicking on Manuals in the Technical Support section and then entering a model number. You can also visit our web site at http://www.agilent.com/find/acqiris. At Agilent we appreciate and encourage customer input. If you have a suggestion related to the content of this manual or the presentation of information, please contact your local Agilent Acqiris product line representative or the dedicated Agilent Acqiris Technical Support (ACOIRIS\_SUPPORT@agilent.com).

# **Acqiris Product Line Information**

USA (800) 829-4444 Asia - Pacific 61 3 9210 2890 Europe 41 (22) 884 32 90

© Copyright Agilent 2009

$\mathsf{Adobe} \circledast \mathsf{and} \mathsf{Acrobat} \circledast \mathsf{are} \mathsf{ trademarks} \mathsf{ of} \mathsf{ Adobe} \mathsf{ Systems} \mathsf{ Incorporated}.$

Windows® is a U.S. registered trademark of Microsoft Corporation.

MATLAB® is a registered trademark of The MathWorks, Inc.

## CONTENTS

| 1. OU       | T OF THE BOX                                                 | 6  |

|-------------|--------------------------------------------------------------|----|

| 1.1.        | Message to the User                                          | 6  |

| 1.2.        | Using this Manual                                            | 6  |

| 1.3.        | Conventions Used in This Manual                              | 6  |

| 1.4.        | Model Names                                                  | 7  |

| 1.5.        | Disclaimer and Safety                                        | 7  |

| 1.6.        | Warning Regarding Medical Use                                | 7  |

| 1.7.        | Packaging and Handling                                       | 7  |

| 1.8.        | Warranty                                                     |    |

| 1.9.        | Warranty and Repair Return Procedure, Assistance and Support |    |

| 1.10.       | System Requirements                                          |    |

| 1.11.       | Transport & Shipping                                         |    |

| 1.12.       | Maintenance                                                  |    |

| 1.12.       | Cleaning                                                     |    |

| 1.13.       | Disposal and Recycling                                       |    |

|             |                                                              |    |

|             | STALLATION                                                   |    |

| 2.1.        | U1091AK02 IC414 Installation                                 |    |

| 2.1         |                                                              |    |

|             | 2. IC414 Windows software installation                       |    |

| 2.2.        |                                                              |    |

| 2.2         | 8                                                            |    |

| 2.2         |                                                              |    |

| 2.2         |                                                              |    |

| 2.3.        | 8                                                            |    |

| 2.3         | 6                                                            |    |

| 2.3         |                                                              |    |

| 2.3         | e                                                            |    |

|             | 3.3.1. Compiling the kernel module                           |    |

| 2.3         | 8                                                            |    |

| 2.3<br>2.3  |                                                              |    |

| 2.3<br>2.4. | Installing the Hardware                                      |    |

| 2.4.        | After Restarting                                             |    |

|             | 1. Windows 2000                                              |    |

| 2.5         |                                                              |    |

| 2.5         | LabVIEW RT                                                   |    |

| 2.0.        | Installing the IVI-COM/C Driver                              |    |

| 2.7.        | Distribution for Windows 2000/XP and Linux                   |    |

| 2.8.        | Distribution for windows 2000/AP and Linux                   | 1/ |

| 3. PR       | ODUCT DESCRIPTION                                            |    |

| 3.1.        | Overview                                                     |    |

| 3.1         |                                                              |    |

| 3.1         | 1                                                            |    |

| 3.1         |                                                              |    |

| 3.1         |                                                              |    |

| 3.1         | 1 0                                                          |    |

| 3.1         |                                                              |    |

| 3.1         | 5                                                            |    |

| 3.2.        | Trigger                                                      |    |

| 3.2         |                                                              |    |

| 3.2         |                                                              |    |

| 3.2         | 66                                                           |    |

| 3.2         |                                                              |    |

| 3.2<br>3.2  |                                                              |    |

| 3.2         | .6. HF Trigger                                               |    |

| 3.2.7          | . Pre- and Post-Trigger Delay                        |  |

|----------------|------------------------------------------------------|--|

| 3.2.8          | . Trigger Status                                     |  |

| 3.3.           | Sampling Rate                                        |  |

| 3.4.           | Data Acquisition - Digitizer Mode                    |  |

| 3.5.           | Data Processing – Analyzer Mode                      |  |

| 3.5.1          | 6                                                    |  |

| 3.5.2          |                                                      |  |

| 3.5.3          | 6                                                    |  |

|                | External Clock and Reference                         |  |

|                | Internal Calibration                                 |  |

|                | External Trigger Output                              |  |

|                | AC210 Front Panel Inputs and Controls                |  |

| 3.10.          | AC240 Front Panel Inputs and Controls                |  |

| 3.11.          | Physical Specifications                              |  |

| 3.11.          |                                                      |  |

| 3.11.          | 2. Environmental and Physical                        |  |

| 4. FIRM        | /IWARE                                               |  |

| 4.1.           | Base Test Firmware                                   |  |

| 4.1.1          | Architecture of Base Test Firmware                   |  |

| 4.1.2          |                                                      |  |

| 4.2.           | FFT Spectrometer Firmware                            |  |

| 4.2.1          | 1                                                    |  |

| 4.2.2          | I/O and Controls of FFT Spectrometer Firmware        |  |

| 5. RUN         | NING THE ANALYZER DEMO APPLICATION                   |  |

|                | Getting Started with Analyzer Demo                   |  |

| 5.2.           | Instrument Control Window                            |  |

| 5.3.           | Digitizer Control Window                             |  |

| 5.4.           | Application Windows & Acquisition Mode               |  |

| 5.5.           | Base Test Application                                |  |

| 5.5.1          | . Register Tests                                     |  |

| 5.5.2          | . Data Transfer Tests                                |  |

| 5.5.3          | . Memory Tests                                       |  |

| 5.6.           | FFT Spectrometer Application                         |  |

| 5.6.1          | . Digitizer Setup                                    |  |

| 5.6.2          | · · · · · · · · · · · · · · · · · · ·                |  |

| 5.6.3          | 1 1 2                                                |  |

| 5.6.4          | . Monitoring                                         |  |

| 6. PRO         | GRAMMING THE FIRMWARE                                |  |

| 6.1.           | Programming Aspects Common to All AC2x0 Applications |  |

| 6.1.1          | . Accessing the DPU Registers                        |  |

| 6.1.2          |                                                      |  |

| 6.1.3          |                                                      |  |

| 6.1.4          | 8 8                                                  |  |

| 6.1.5          |                                                      |  |

| 6.1.5          | 8 8                                                  |  |

| 6.1.5          |                                                      |  |

| 6.1.5          |                                                      |  |

| 6.1.5<br>6.1.5 | 3                                                    |  |

| 6.1.5          |                                                      |  |

| 6.1.6          | 11 6                                                 |  |

|                | Registers in the Base Test and FFT firmware          |  |

| 6.2.1          | -                                                    |  |

| 6.2.2          | •                                                    |  |

| 6.2.2          | <u> </u>                                             |  |

| 6.2.2          |                                                      |  |

| 6.3 | . Prog                                                 | gramming the FFT Spectrometer Application                   |    |

|-----|--------------------------------------------------------|-------------------------------------------------------------|----|

| (   | 5.3.1.                                                 | Configuring the Data Processing Unit                        |    |

| (   | 6.3.2. Computing and Loading the (optional) FFT Window |                                                             |    |

| (   | 5.3.3.                                                 | Reading Accumulated Spectra                                 |    |

| (   | 5.3.4.                                                 | Normalizing the Accumulated Spectra                         |    |

|     | 6.3.4.1.                                               | Normalizing the Raw Data                                    |    |

|     | 6.3.4.2.                                               | Converting the Spectra to dBc Full Scale                    |    |

| (   | 5.3.5.                                                 | Checking on Overflows                                       |    |

| (   | 5.3.6.                                                 | Stopping the FFT Spectrometer                               |    |

| (   | 5.3.7.                                                 | Synchronizing with other Equipment (e.g. Telescope)         |    |

| (   | 5.3.8.                                                 | Registers in FFT Spectrometer Firmware                      |    |

|     | 6.3.8.1.                                               | Indirect Access Port                                        | 54 |

|     | 6.3.8.2.                                               | Indirect Address Register                                   | 54 |

|     | 6.3.8.3.                                               | Buffer Identifier Register                                  | 54 |

|     | 6.3.8.4.                                               | Acqiris Control Register                                    | 55 |

|     | 6.3.8.5.                                               | Code Protection Register                                    | 55 |

|     | 6.3.8.6.                                               | Acqiris Status Register                                     | 55 |

|     | 6.3.8.7.                                               | TempMonitor                                                 |    |

|     | 6.3.8.8.                                               | DEControl Register                                          | 56 |

|     | 6.3.8.9.                                               | Main Control Register                                       | 56 |

|     | 6.3.8.10.                                              | Status Register                                             | 57 |

|     | 6.3.8.11.                                              | Accumulator Counter                                         |    |

|     | 6.3.8.12.                                              | FFT Configuration Register                                  |    |

|     | 6.3.8.13.                                              | Front Panel µDB I/O Register                                | 59 |

|     | 6.3.8.14.                                              | Clear Buffer Register                                       | 59 |

|     | 6.3.8.15.                                              | Overflow Status Register                                    | 60 |

|     | 6.3.8.16.                                              | ADC Overflow Counter Register                               | 60 |

| 7.  | APPENI                                                 | DIX A: U1093A (U1056A) AS BUS FOR COMPACTPCI/PXI DIGITIZERS | 61 |

# 1. Out of the Box

#### **1.1.** Message to the User

Congratulations on having purchased an Agilent Technologies Acqiris data conversion product. Acqiris Digitizers /Analyzers are high-speed data acquisition modules designed for capturing high frequency electronic signals. To get the most out of the products we recommend that you read this manual carefully. We trust the product you have purchased will meet with your expectations and provide you with a high quality solution to your data conversion applications.

#### **1.2.** Using this Manual

The AC240 and AC210 analyzer platforms are dual- and single-channel 6U CompactPCI<sup>®</sup>/PXI<sup>TM</sup> 1 GS/s per channel digitizers with on-board real-time data processing.

The Analyzer functions are dependent on the firmware code loaded into the Data Processing Unit. They are described in this manual throughout the Firmware sections.

This guide assumes you are familiar with the operation of a personal computer (PC) running a Windows 2000/XP or other supported operating system. It also assumes you have a basic understanding of the principles of data acquisition using either a waveform digitizer or a digital oscilloscope.

The manual is divided into 6 separate sections. To understand the elements of operation for the module it is essential that you carefully read chapters 1-5.

- Chapter 1 **OUT OF THE BOX,** describes what to do when you first receive your new Acqiris product. Special attention should be paid to sections on safety, packaging, and product handling. Before installing your product please ensure that your system configuration matches or exceeds the requirements specified.

- Chapter 2 *INSTALLATION*, covers elements of installation. Before attempting to use your Acqiris product for actual measurements we strongly recommend that you read all sections of this chapter.

- Chapter 3 **PRODUCT DESCRIPTION**, provides a short description of all the functional elements of the AC210 and AC240 Modules.

- Chapter 4 *FIRMWARE*, provides a detailed description of the Base Test and FFT Spectrometer firmware including algorithm and implementation aspects.

- Chapter 5 **RUNNING THE ANALYZER DEMO** Application describes the operation of the Analyzer Demo application. Analyzer Demo allows interactive operation of the AC240/AC210 from a PC running a Windows 2000/XP operating system.

- Chapter 6 **PROGRAMMING THE FIRMWARE,** provides all the information required to write a software application based on the FFT Spectrometer firmware.

For information necessary for writing your own software to control Acqiris products you should also refer to the **Programmer's Guide** and the **Programmer's Reference Manual**.

## **1.3.** Conventions Used in This Manual

The following conventions are used in this manual:

|                    | This icon to the left of text warns that an important point must be observed.                                        |

|--------------------|----------------------------------------------------------------------------------------------------------------------|

| WARNING            | Denotes a warning, which advises you of precautions to take to avoid being electrically shocked.                     |

| CAUTION            | Denotes a caution, which advises you of precautions to take to avoid electrical, mechanical, or operational damages. |

| NOTE               | Denotes a note, which alerts you to important information.                                                           |

| Italic             | text denotes a warning, caution, or note.                                                                            |

| <b>Bold Italic</b> | text is used to emphasize an important point in the text or a note                                                   |

| mono               | text is used for sections of code, programming examples, and operating system commands.                              |

| B,KB,MB,GB | is for Byte, KiloByte = 1024 bytes, MegaByte = 1024*1024 bytes, GigaByte = 1024*1024*1024<br>bytes |

|------------|----------------------------------------------------------------------------------------------------|

| b,Kb,Mb    | is for bit with multipliers as above.                                                              |

| Triggered  | Denotes a VHDL object. It could be a single- or multi-bit signal or a component or a library name. |

| 0xnn       | Denotes a hexadecimal value.                                                                       |

## 1.4. Model Names

Agilent Technologies Inc. acquired Acqiris SA and its product lines in December 2006. Use the tables below to cross reference the legacy model name and new Agilent numbers

| Agilent Model Number | Acqiris Model Name |

|----------------------|--------------------|

| U1091AAC1            | AC210              |

| U1080A-001           | AC240              |

## 1.5. Disclaimer and Safety

The AC Series CompactPCI Analyzer cards have been designed to operate in a CompactPCI/PXI crate. Power for the modules is provided by plugging them into a free slot (refer to the installation procedure). Agilent Technologies does not recommend operation of the AC210 or AC240 outside of a CompactPCI/PXI crate

**CAUTION:** Do not exceed the maximum input voltage rating! The maximum input voltage for 50  $\Omega$  input impedance is  $\pm 5$  V.

## 1.6. Warning Regarding Medical Use

The AC Series CompactPCI Analyzer cards are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of these cards involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user. These cards are **not** intended to be a substitute for any form of established process or equipment used to monitor or safeguard human health and safety in medical treatment.

WARNING:

/!\

The modules discussed in this manual have not been designed for making direct measurements on the human body. Users who connect an Acqiris module to a human body do so at their own risk.

## 1.7. Packaging and Handling

Your Analyzer is shipped with the following components:

- A compact disc in an Agilent Technologies paper CD envelope that includes

- 10 product User Manuals in electronic form (8-bit Digitizers, 10-bit Digitizers, 12-bit Digitizers, Averagers, Analyzers, Signal Analyzers, Streamer Analyzers, Time-to-Digital Converters, 3-, 5-, and 8-slot CompactPCI Crates, and the 21-slot CompactPCI Crate),

- o 1 Programmer's Guide and 1 Programmer's Reference Manual,

- o device drivers with sample software for different operating systems, environments and languages,

- o the Analyzer Demo application, a demonstration program for the AC/SC Analyzer products,

- o the AcqirisLive application, a demonstration program for our digitizer and averager products,

- o the SSR Demo application, a demonstration program for the Acqiris AP235/AP240 Analyzers,

- o the APX01 Demo application, a demonstration program for the Acqiris AP101/AP201 Analyzers,

- the TC Demo application, a demonstration program for the Acqiris TC840/TC842/TC890 Time-to-Digital Converters,

- full installation procedures for use with Microsoft Windows, National Instruments LabVIEW RT, Wind River VxWorks, IVI-COM/C, and Linux software.

- A declaration of conformity

- Optional documentation such as a model-dependent document giving Specifications & Characteristics, a Calibration Certificate, or a Performance Verification

After carefully unpacking all items, inspect each to ensure there are no signs of visible damage. Also check that all the components received match those listed on the enclosed packing list. Agilent cannot accept responsibility for missing items unless we are notified promptly of any discrepancies. If any items are found to be missing or are received in a damaged condition please contact the Agilent service center or your local supplier immediately. Retain the box and packing materials for possible inspection and/or reshipment.

## 1.8. Warranty

All Agilent Acqiris Digitizer products are warranted to operate within specification, assuming normal use, for a period of at least one year from the date of shipment. Units sold before April 2008 had three year warranties, as do some more recent ones; in case of doubt examine your invoice. It is recommended that yearly calibration be made in order to verify product performance. All repairs, replacement and spare parts are warranted for a period of 3 months. Warranty extensions are available as an option.

Agilent endeavors to provide leading edge technology that includes the latest concepts in hardware and software design. As such software and firmware used with the products is under continual refinement and improvement. All software and instrument firmware is supplied "as is" with no warranty of any kind. Software and firmware is thoroughly tested and thought to be functional at the time of shipment. At Agilent's discretion software and firmware may be revised if a significant operational malfunction is detected.

In exercising this warranty, Agilent will repair or replace any product returned to the Agilent service center, within the warranty period. The warranty covers all defects that are a result of workmanship or materials. This excludes defects that are caused by accident, misuse, neglect, or abnormal operation.

The purchaser is responsible for returning the goods to the nearest Agilent service center. This includes transportation costs and insurance. Agilent will return all warranty repairs with transportation prepaid.

## 1.9. Warranty and Repair Return Procedure, Assistance and Support

Agilent acquired Acqiris SA and its product lines in December 2006. Please contact your nearest Agilent Service Center before returning any product for repair.

You can find information about technical and professional services, product support, and equipment repair and service on the Web, see <u>http://www.agilent.com/find/service</u> (or <u>http://www.agilent.com/</u> and after selecting your country click on **Contact Us**). The service center will ask for your name, company, phone number and address, the model and serial numbers of the unit to be repaired, and a brief description of the problem.

Before issuing a Service Order the service center may ask you to communicate with us by phone or eMail so that we can learn as much as needed about the problems observed. If a unit returned under guarantee is found to be working normally and this procedure was not followed we reserve the right to charge you for the work done.

For your nearest customer support center please contact Acqiris Technical Support (ACQIRIS\_SUPPORT@agilent.com) or come visit our web site at <a href="http://www.agilent.com/find/acqiris">http://www.agilent.com/find/acqiris</a>. Alternatively, contact Acqiris at 1-800-829-4444 in the USA, +41 22 884 32 90 in Europe or +61 3 9210 2890 in the Asia-Pacific region. The Agilent Support Centers can also help redirect you for any questions concerning the installation and operation of your equipment.

## 1.10. System Requirements

Acqiris products need the following minimum PC System Requirements in order to obtain reasonable performance from the module:

**Processor:** 150 MHz Pentium (higher recommended). Some PowerPC systems running Wind River VxWorks are supported; please contact us for details.

Memory: 256 MB RAM. This number is a very rough estimate.

**Display resolution:** At least 1280 x 1024 pixels and 256 colors for use of the Analyzer Demo program is strongly recommended.

**Operating System:** Microsoft Windows 2000/XP including 2003 Server, Wind River VxWorks 5.5.1 and 6.4, and Linux with kernels 2.4 and 2.6. Support for Windows 95/98 is no longer available. Although this operating system is no longer supported by Microsoft, Windows NT4 users can download AcqirisSoftware 3.1 from the Agilent WEB site.

#### Hard Drive Space: 20 MB Minimum

**CD Drive** (or any method to copy the software installation files from CD to the hard drive such as LAN, floppy drive, etc.)

LabVIEW: Full driver implementations are available for National Instruments LabVIEW versions 8.5, 8.2.1, and 8.0. LabVIEW 7.1 is frozen at the level of Acqiris Software 3.2 with support for all instruments.

LabVIEW RT: National Instruments LabVIEW RT is supported for the same versions as shown above. The VISA driver must be version 3.0 or higher.

MATLAB: The MEX interface can be used with MathWorks MATLAB 7.3 or a newer version.

Visual BASIC: The interface files and examples are available for Microsoft Visual Basic .NET and Version 6.

Tornado: The example files are useable with Wind River Tornado 2.2.1

## 1.11. Transport & Shipping

**CAUTION:** Cards can be safely transported in their original shipping packages. DC cards can be transported when properly mounted in a CompactPCI crate.

To package the instrument for shipping:

#### Step

Notes

**1.** Place the instrument in its original packaging materials.

**2.** Surround the instrument with at least 3 to 4 inches (8 to 10 cm) of its original packing material or bubble-pack to prevent the instrument from moving in its shipping container.

**3.** After wrapping it with packing material, place the instrument in its original shipping container or a strong shipping container that is made of double-walled corrugated cardboard with 159 kg (350 lb) bursting strength.

**4.** Seal the shipping container securely with strong nylon adhesive tape.

**5.** Mark the shipping container "FRAGILE, HANDLE WITH CARE" to help ensure careful handling.

**6.** Use the address obtained from your Agilent Technologies Service Center.

7. Retain copies of all shipping papers.

**CAUTION:** Damage can result if the original packaging materials are not used. Packaging materials should be anti-static and cushion the instrument on all sides. NEVER USE STYRENE PELLETS IN ANY SHAPE AS PACKAGING MATERIALS. They do not adequately cushion the instrument or prevent it from moving in the shipping container. Styrene pellets can also cause equipment damage by generating static electricity or by lodging in fan motors.

#### 1.12. Maintenance

The cards do not require any maintenance. There are no user serviceable parts inside. A periodic calibration can be obtained on request.

#### 1.13. Cleaning

Cleaning procedures consist only of exterior cleaning.

Clean the exterior surfaces of the module with a dry lint-free cloth or a soft-bristle brush. If any dirt remains, wipe with a cloth moistened in a mild soap solution. Remove any soap residue by wiping with a cloth moistened with clear water. Do not use abrasive compounds on any parts.

#### 1.14. Disposal and Recycling

Electronic equipment should be properly disposed of. Acqiris Digitizers and their accessories must not be thrown out as normal waste. Separate collection is appropriate and may be required by law.

• If the original packaging materials are not available, use a professional packaging service. Contact your Agilent Service Center for more information.

• The shipping container must be large and strong enough to accommodate your instrument and allow at least 3 to 4 inches (8 to 10 cm) on all sides for packing material.

# 2. Installation

This chapter describes how to install the Acqiris hardware and software for Windows 2000/XP, National Instruments LabVIEW RT, Linux, or Wind River VxWorks.

**NOTE:** For a first time installation we strongly recommend installing the software **before** inserting the hardware into the PC.

## 2.1. U1091AK02 IC414 Installation

**NOTE:** If you are going to install an IC414 interface for the first time and are running Windows 2000/XP you should follow the procedure below **before** installing the Acqiris hardware.

#### 2.1.1. IC414 Hardware installation hints

The PCI-8570/PXI-8570 User's Manual (Rev. 1.00) section 2.5 gives Hardware Installation instructions.

**CAUTION:** Turn off the power of the PC; the PC may have to be unplugged to ensure that the PCI bus has no power available. Please ignore the PCI-8570 instruction to leave the power cord plugged in; Ground the chassis differently!

$\wedge$

#### **CAUTION:** Touch the antistatic package to a grounded object before removing the card from the package. Electrostatic discharge can damage the card.

The standard cable pair provided each have a red connector on one end and a black connector on the other. Therefore the correct connection can be made by plugging the Red connector into the LORx socket and the Black connector into the LOTx socket on the PXI module and the other Red connector into the PCI module socket furthest from the PCI card internal base connector and the Black connector into the next socket.

If you intend to use 64-bit 66 MHz transfer to maximize data transfer speed you should cable a "bundled link" using two standard cable pairs and both the L0 and L1 pairs of connectors. You should also make sure that you configure the PXI-8570 M66EN Jumper correctly.

#### 2.1.2. IC414 Windows software installation

Linux users do not need to read any further since there is no special software installation.

Windows users should have the hardware installed as noted above. This software installation should be done before any Acqiris modules are placed in the CompactPCI crates. This may mean that you have to remove the module from the crate *as delivered*.

The crate should be turned on first followed by the PC. If the cabling and start-up sequence is done correctly there will be no LED illuminated on the PCI unit connected pair and the LED's of the PXI connected pair will be lit.

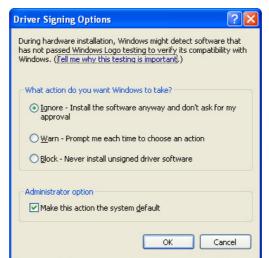

For Windows XP installation, Select the Control Panel under Settings in the Start menu. Then, if you are using the Category View select Printers and Other Hardware. After this, for both Category and Classic views, go to System and then display the Hardware tab to get access to the Driver Signing menu. Since neither the AdLink nor the Acquiris driver has been submitted for Windows Logo testing you must select either the Ignore or Warn action. The resulting menu looks as shown:

The PCI-8570/PXI-8570 User's Manual (Rev. 1.00) section 2.4 contains the software installation instructions. These should be executed before allowing the hardware installation process to look for the driver. If you have an AdLink CD Version 2004A4 or later you can use it; if not you should download the latest driver from the WEB site (http://www.adlinktech.com/). You can then continue with the Hardware Installation. A reboot will then be necessary. At this point the Stargen Fabric PCI Adapter and the Stargen Aruba Fabric-to-PCI Bridge should appear correctly installed under System Devices in the Device Manager.

*NOTE:* If you have an AdLink CD Version 2005A3 or later you can find 8570install.exe in the folder X:\Driver Installation\PXI Platform\PXI Extension\PCI\_PXI-8570\Wnt2kxp and the starfab1.inf file in the folder X:\Driver Installation\PXI Platform\PXI Extension\PCI\_PXI-8570\Win98.

## 2.2. Installing the Software under Windows

#### 2.2.1. Warnings

If Setup detects a previous installation of Acqiris software on your system, a warning screen will be displayed. It is recommended to exit Setup and uninstall older versions.

The installer from software releases prior to **Acqiris Software 2.0** installed the Digitizer Driver DLL files into the System directory. These will be removed by Setup. If you wish to keep the old installation on your system, you should exit Setup, and move all Acqiris driver files (acqiris\*, acqrs\* and acqir\*) to some archive directory.

The DLL files will be installed into the bin subdirectory of the Acqiris software root, and the corresponding path will be added to the PATH environment variable.

#### 2.2.2. Multiple Versions

With the software installation from **Acqiris Software 2.0** (or above), it is possible to keep multiple versions on the same system, but you must specify a different root directory (i.e. Install Folder). If you keep the same directory, Setup will overwrite your previous installation.

To go back to a previous version, you must change the PATH environment variable and reinstall the Kernel driver. Under Windows 2000/XP:

- 1. Copy the SYS file from <old\_AcqirisSoftware\_root>\bin\kernel to the Windows\System32\drivers directory.

- 2. Change the AcqirisDxRoot, AcqirisDxDir and PATH environment variables to the old root.

- 3. Reboot the computer.

#### 2.2.3. Installation

Before installing the Acqiris hardware, you should complete the following steps to install the software for Windows 2000/XP.

**NOTE:** You will need administrator privileges to complete the software installation under Windows 2000/XP.

- 1. Insert the *Acqiris Software CD* into the CD-ROM drive of your computer. If the Autorun program does not start automatically (Autoplay disabled), you can start it manually, or navigate to the *AcqirisSoftware\Windows* folder in order to display the files included.

- 2. Choose Install AcqirisSoftware for Windows 2000/XP/2003 Server (or run Setup.exe from the *AcqirisSoftware*\Windows folder). After several seconds for initialization the first of many screens will appear.

Please note the following points:

- It is good practice to remove any previously installed version of Acqiris software. If the program finds that there is still Acqiris software installed on your machine a warning panel will appear.

- In the Select Install Type window selecting Custom installation will let you select individual packages for loading. The space indicated for LabVIEW, Firmware and UserManual packages is incorrect. The correct values are 7 MB, 40 MB, and 30 MB respectively. A full installation requires just under 150 MB of disk.

- If MATLAB is installed on your machine, you will be asked to point the installer to the MATLAB root directory. You should do this if you want the installer to modify the standard startup.m file to add the paths for the MEX interface.

- In the **Installation Folder** window you will give the name of the root directory of the Acqiris software installation. If User Manuals (30 MB) and Firmware (40 MB) are loaded more space than indicated here will be required on the drive. For the case of a Tornado 2.2 installation the folder name should not contain any spaces.

- AcqirisLive needs the LabWindows/CVI 8.0 Run-Time Engine to run. If Setup has detected that a

LabWindows/CVI Run-Time Engine is already installed on your system, it will ask you if you would like to

install it locally for AcqirisLive anyway. If you are not sure about the version of the CVI Run-Time Engine

on your system, it is recommended to install it locally.

- The **Installation Summary** window will be shown to allow you to check what you have asked for. At this point it is not too late to go back and make changes. The actual installation will only be started after clicking on "Install" in the next window.

- Please read the **IMPORTANT Information** window text. It could help you avoid serious problems.

- Registration of your installation will help Agilent provide you with better support. You will also be notified of updates and upgrades. All information submitted will be treated in accordance with Agilent's privacy policy. Setup will prepare a registration e-mail in your e-mail client application upon termination of the setup procedure. You can then decide whether or not you wish to send it. You may also add comments. Uncheck the box if you do not want to register your installation.

- After the software installation is complete you can either accept the suggestion to restart the computer or you should shutdown your computer and proceed with the hardware installation.

## 2.3. Installing the Software for Linux

The Acqiris software is ready to install on Linux systems running kernels 2.4 and 2.6; package files are now available for some popular distributions. If you are using Debian, Ubuntu, Fedora, CentOS, or openSUSE, you can install the software using a standard package: see section 2.3.2 **Installing with a distribution specific package**.

## 2.3.1. Installing with a tar file

The following archives all contain the driver and library compiled with the gcc version shown:

AcqirisLinux-3.3a-gcc-3.4.tar.gz - compiled under CentOS 4.7 with GNU gcc 3.4.

AcqirisLinux-3.3a-gcc-4.1.tar.gz - compiled under Debian 'etch' 4.0 with GNU gcc 4.1.

The appropriate tar file should be copied to a local directory (e.g. your home directory) and then unpacked by using the following command

tar xzf AcqirisLinux-3.3a-gcc-X.x.tar.gz

The resulting directory AcqirisLinux contains an install script drv-install and a graphical Demo program demo/AcqirisDemo. Before running the software you have to install the acqrsPCI device driver into the running kernel

## 2.3.2. Installing with a distribution specific package

The distribution specific package files are located in directories named after the distribution name and version. Packages are available for the following variants:

• Debian, 4.0, 5.0 - the distribution used for the development of Acqiris software.

Debian-4.0/agilent-acqirisdriver\_3.3a-1\_i386.deb

Debian-5.0/agilent-acqirisdriver\_3.3a-1\_i386.deb

• Ubuntu, 8.04, 8.10 - this is the most popular and easy-to-use distribution, based on Debian.

Ubuntu-8.04/agilent-acqirisdriver\_3.3a-1\_i386.deb

Ubuntu-8.10/agilent-acqirisdriver\_3.3a-1\_i386.deb

• Fedora, 10 - another popular innovative distribution, test bed for RedHat Linux.

Fedora-10/agilent-acqirisdriver-3.3a-1.i386.rpm

• CentOS, 4.7, 5.2 - this distribution is a rebranded build of RedHat Enterprise Linux.

CentOS-4.7/agilent-acqirisdriver-3.3a-1.i386.rpm

CentOS-5.2/agilent-acqirisdriver-3.3a-1.i386.rpm

- openSUSE, 11 this distribution is the base system for Novell SUSE Linux.

- openSUSE-11/agilent-acqirisdriver-3.3a-1.i586.rpm

More information on these distributions is available on the following web-site: http://distrowatch.com/dwres.php?resource=major

All these packages contain a version of the software Acqiris 3.3a release for Linux with full support of recent Acqiris products.

A deb package should be installed by the root user with the following command:

dpkg -i agilent-acqirisdriver\_3.3a-1\_i386.deb

An rpm package should be installed by the root user with the following command:

rpm -ivh agilent-acqirisdriver-3.3a-1.i386.rpm

Before being able the run the software, you have to install the acqrsPCI device driver into your running kernel as described in the next section.

#### 2.3.3. Installing the Linux device driver

The acqrsPCI device driver is a loadable kernel module. It is provided as source files.

#### 2.3.3.1. Compiling the kernel module

All files needed to compile a new kernel mode driver are in

- src/agilent/acqiris/kernel26module/ for Linux kernels 2.6,

- or src/agilent/acqiris/kernel24module/ for Linux kernels 2.4.

To compile the driver, the header files of the Linux kernel need to be installed. Furthermore, depending on the Linux distribution, the kernel source files may need to be installed too.

For Debian users, in order to compile the kernel module on a system, the kernel packages that match the current kernel-image must be installed. For instance, on a Debian 'etch' 4.0 system 686 the required packages are:

```

linux-image-2.6-686

linux-image-2.6.18-4-686

linux-headers-2.6-686

linux-headers-2.6.18-4

linux-headers-2.6.18-4-686

linux-kbuild-2.6.18

```

The makefile will try to guess where the kernel headers are located. If it fails, see instructions inside the makefile itself to specify manually where these kernel header files are located.

To compile a new kernel module, use the following commands:

| cd kernel26module | (or kernel24module)                                 |

|-------------------|-----------------------------------------------------|

| make clean all    | to generate a new kernel module from scratch        |

| make install      | to copy the kernel module where it should reside    |

|                   | (this last command requires super user privileges). |

In the end, the loadable kernel module should be present in the system's loadable kernel modules directory. You can verify it is present by running:

ls -l /lib/modules/\$(uname -r)/extra/acqrsPCI.ko

Note that this version of the loadable kernel module had been tested on Linux kernel versions up to 2.6.27. However, starting with kernel 2.6.17, a few kernel functions relating to the device classes are no longer available to proprietary modules (such as this one). As such, automatic creation of the /dev/acqrsPCI node has to be done manually in the /etc/rc.local file (see **Creating the device driver node** in 2.3.4 **Loading the kernel module**).

## 2.3.4. Loading the kernel module

Once the device driver is installed into its kernel module directory, it has to be loaded into the kernel. First update the kernel modules dependencies:

/sbin/depmod -a

Then load the kernel module:

/sbin/modprobe -v acqrsPCI

You can add the command above to your /etc/rc.local file. It is run at system startup and will load the acqrsPCI kernel module automatically when your computer is restarted.

You can check that the device driver is loaded properly with lsmod.

/sbin/lsmod | grep acqrsPCI

If lsmod does not report a module named acqrsPCI, then the kernel module is not loaded into the kernel. Check any error messages that may have been issued by the commands you have run, and contact Agilent Acqiris technical support.

#### 2.3.5. Creating the device driver node

Check that a device node has been created.

ls -l /dev/acqrsPCI

If the device node /dev/acqrsPCI is present on your system, the Acqiris Software is ready to be used. Otherwise, continue reading this section.

For systems using udev (the dynamic /dev/ hierarchy) or running kernels above 2.6.17, the device driver node may not be created automatically. You can do it with mknod by running the following command:

/sbin/mknod -m 666 /dev/acqrsPCI c 124 0

You can check that the device node has been created with ls:

ls -l /dev/acqrsPCI

You can add the mknod command to your /etc/rc.local file. It is run at system startup and will create the /dev/acqrsPCI device node automatically when your computer is restarted.

Note that the permissions that are set in this example (-m 666) give access to the Acqiris instruments to all users. This may not be what you expect and these permissions can be adjusted to fit your requirements. The base rule is that any user that wants to use the Acqiris instruments have to get read and write access to /dev/acqrsPCI.

## 2.3.6. Firmware files and Environment variables

If you intend to use Averagers, Analyzers, Time to Digital converters, or 12-bit digitizers you must install the Firmware .bit files. You can either copy them from the Firmware directory of the CD-ROM or download them from our WEB site. They should be placed in the Firmware subdirectory of AcqirisLinux. In the case of the CD-ROM, this can be done by continuing the above command sequence with the following:

cp /mnt/CDRom/Firmware/\*.bit Firmware/

If you need to keep multiple versions of the Firmware, please continue reading this section.

Automatic loading of the firmware needed by some modules relies on the environment variable AcqirisDxDir pointing to the directory containing the file AqDrv4.ini which in turn points to the directory containing the Firmware .bit files. Therefore, assuming that your Firmware is in /usr/local/AcqirisLinux/Firmware and that AqDrv4.ini is in /usr/local/AcqirisLinux/demo then you must edit AqDrv4.ini so that it contains the line

#### fpgaPath=/usr/local/AcqirisLinux/Firmware

Then, if your shell is csh or tcsh modify the .login file to contain the line

#### setenv AcqirisDxDir /usr/local/AcqirisLinux/demo

or, if your shell is **bash**, **ksh**, **zsh** or **sh**, modify the **.profile** file to contain the lines

#### AcqirisDxDir=/usr/local/AcqirisLinux/demo

export AcqirisDxDir

#### 2.4. Installing the Hardware

- 1. Turn off the power of the PC and the crate in the case of a CompactPCI module.

- **CAUTION:** For PCI modules the PC may have to be unplugged to ensure that the PCI bus has no power available. However, CompactPCI crates can be left plugged in since this ensures proper grounding.

#### **CAUTION:** Touch the antistatic package to a grounded object before removing the card from the package. Electrostatic discharge can damage the card.

2. <u>Module in a PC:</u> open the PC, identify a free PCI slot and carefully insert the DP Series card into it. Be sure to ground yourself by touching the grounded PC frame and avoid touching any components on the DP Series card. Make sure that the grounding of the card's mounting bracket to the back panel rail of the computer is done correctly. If present make sure that the fan's adjustable retainer is correctly positioned and tightened for mechanical support. Close the PC.

<u>Module in a CompactPCI crate:</u> Follow the instructions of the crate manufacturer to insert the DC Series card into a free 6U CompactPCI peripheral slot. Be sure to ground yourself by touching the grounded crate and avoid touching any components on the DC Series card. Be sure to tighten both front panel mounting screws to lock the module into place and insure proper grounding of the frame.

**NOTE:** To ensure the best possible performance, users of Acqiris CC121 Crates with AS bus systems should respect the module placement rules to be found in the Agilent Acqiris 21-slot CompactPCI Crate User Manual.

<u>PCI Bus extension module in a PC</u>: Consult the manufacturer's documentation for any special instructions. Open the PC, identify a free PCI slot and carefully insert the card into it. Be sure to ground yourself by touching the grounded PC frame and avoid touching any components on the card. Make sure that the grounding of the card's mounting bracket to the back panel rail of the computer is done correctly. Close the PC. Connect the module to the CompactPCI crate controller.

3. Turn on the power of the crate(s), if present, and then the PC and start the operating system.

**NOTE:** Acqiris modules are equipped with a LED. If this LED is not glowing orange or red when the power is applied there is a severe problem. Either the module is broken or the necessary voltages for its use are not available.

**NOTE:** For proper system operation when using the IC200, IC414, or other PCI extension interface to connect a CC10X crate to a remote PC, the crate **must** be powered on before the PC in order for the PC BIOS to recognize the presence of the CompactPCI crate.

4. If devices were installed using a previous version of Acqiris software the instruments in these logical positions may still appear as *Unknown Devices*. This can be changed to the new Acqiris type category with the Grey Diamond icon by **Uninstall**ing the device and then **Installing** again. Instructions on this procedure can be found in the **ReadMe.txt** file in the **manuals** folder of your Acqiris software installation.

## 2.5. After Restarting

## 2.5.1. Windows 2000

Under Windows 2000, you *must* login with administrator privileges after the first boot following the hardware installation; the Plug&Play system must have the appropriate privileges to be able to complete your hardware installation successfully. After a successful hardware installation, you will be able to use your Acqiris module(s) with normal privileges.

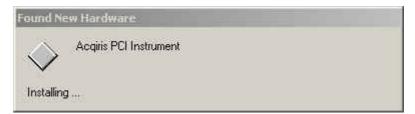

At the first boot following the hardware installation, Windows will detect the new hardware and will install the devices automatically. The following image will appear.

**NOTE:** In some systems an application program (such as AcqirisLive) will not yet work correctly at this point. One additional boot cycle may be needed if this is the first time that a hardware board is being installed.

# 2.5.2. Windows XP

Under Windows XP, you *must* login with administrator privileges after the first boot following the hardware installation; the Plug&Play system must have the appropriate privileges to be able to complete your hardware installation successfully. After a successful hardware installation, you will be able to use your Acqiris digitizer(s) with normal privileges.

If you login with administrator privileges after the first boot following the hardware installation, Windows will detect the new hardware and start the "Found New Hardware Wizard" after a few seconds. There is no need to use Windows Update to search for the software. You can "Install the software automatically". The final screen should appear as shown here:

**NOTE:** In some systems an application program (such as AcqirisLive) will not yet work correctly at this point. One additional boot cycle may be needed if this is the first time that a hardware board is being installed.

## 2.6. LabVIEW RT

During program development you can choose whether you use LabVIEW or LabVIEW RT compatible libraries by switching the version present in National Instruments\LabVIEW m.n\instr.lib\. This swap can be facilitated by using the Install VI library for LabVIEW or LabVIEW Real-Time shortcut available in the Shortcut folder under Start  $\rightarrow$  Programs.

There is only one Acqiris Driver. It supports all Acqiris Instruments. The instructions below concern LabVIEW RT as used in NI PXI processors.

The Aq\_RT.inf and AqRT\_4.ini files must be uploaded to the target. To do this,

- start the MAX application,

- right click on the target

- select file transfer

- select the Aq\_RT.inf file on your host machine and upload ('To Remote') to the LabVIEW RT working directory (/NI-RT/system) on the target

- select the Aq\_RT.ini file on your host machine and upload ('To Remote') to the LabVIEW RT working directory (/NI-RT/system) giving it the name AqDrv4.ini

For Acqiris modules which need FPGA files you should,

- create the folder \firmware in the /NI-RT/system directory using the file transfer application

- select the FPGA files (from <AcqirisDxRoot>\Firmware) you want to copy to the target and upload them into the firmware directory

Restart the target after finishing the file transfers.

Restart the MAX Explorer and you should have Acqiris digitizers detected in your PXI system.

## 2.7. Installing the IVI-COM/C Driver

Please install Acqiris software for Windows first. Then the *Acqiris Software CD* Autorun program gives access to two installers:

- IVI Shared Components 1.4

- IVI-COM/C IviAqD1 driver

These must be installed in the order shown above. For more information you can then consult the Readme.txt file in the IVI\Drivers\IviAqD1 folder or the documentation through the program shortcut present under Ivi/IviAqD1.

## 2.8. Distribution for Windows 2000/XP and Linux

The manuals/ReadMe.txt file contains a list of files to be found after a complete installation of Acqiris software on Windows systems. Similarly the ReadMeLinux file gives the list of files corresponding to that installation.

# **3. Product Description**

## 3.1. Overview

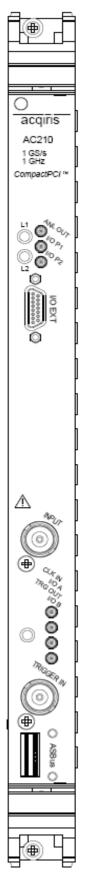

The AC Series are powerful analyzer platforms based on a single-channel (AC210) or dual channel (AC240) 1 GS/s per channel, 8-bit CompactPCI digitizer with on-board real-time data processing implemented with the aid of a large field-programmable gate array (FPGA).

The AC Series Architecture offers a convenient way to implement user defined data processing algorithms with data rates of up to 2 GS/s. It provides external processing control through dedicated connectors and visual reference by means of two front-panel LEDs.

#### **Key Features**

- **Dual-Channel Performance with Interleave** The AC240 offers dual-channel synchronicity for I/Q acquisitions with up to 1 GS/s sample rate. Interleaved single-channel mode up to 2 GS/s on either input is software selectable. The AC210 provides a single input channel with a sample rate of up to 1 GS/s.

- **On-board reconfigurable Data Processing Unit (DPU)** The AC Series analyzer platform can easily be reconfigured to perform a variety of user-defined on-board real-time signal processing tasks on the digitized signals. The on-board FPGA is capable of executing multiplications in less than 5 ns and offers more than 74,000 logic cells, up to 7 Mbits of on-chip RAM, and 328 dedicated 18-bit x 18-bit multipliers with 36-bit results.

- **Optional external Processing Memory** As an option, the AC Series can be equipped with additional memory to extend the processing capability of the DPU. The P512M Memory option offers two independent banks of 256 MB of DDR333-SDRAM and a 1 MB dual-port SRAM.

- Front-panel I/O Connectors and Controls for real-time data processing control (DPU Ctrl<sup>2</sup>) It provides several front-panel connectors for real-time control of the DPU. The function of these connectors and LEDs is user defined through the implemented firmware.

## 3.1.1. Coupling & Impedance

Each channel has a 50  $\Omega$  signal input BNC connector giving high quality termination with better than  $\pm 1\%$  precision. It is ideally suited for use with 50  $\Omega$  transmission lines. Both AC and DC coupling modes are available. The AC mode couples signals capacitively thus removing the input signal's DC component and filtering out any signal component below 32 Hz. The DC mode allows all signal components to be passed through to the digitizer.

## **3.1.2. Input Protection**

The input amplifiers are fully protected against over-voltage signals. Input signals up to  $\pm 5$  V DC at 50  $\Omega$ , can be input without damaging the front-end electronics.

## 3.1.3. Mezzanine Front-end

The front-end electronics are all mounted on a removable mezzanine card. In the event of accidental damage, or as components fatigue over time (e.g. relays in high duty cycle automated testing applications), the mezzanine card allows for fast and efficient replacement.

## 3.1.4. Bandwidth and Rise Time

The bandwidth specification indicates the frequency at which an input signal will be attenuated by 3 dB (approximately 30% loss of amplitude). The bandwidth also affects the minimum rise and fall times that can be passed through the front-end electronics. A pulse with a very sharp edge will be observed to have a minimum rise time ( $\tau_{min}$ ) determined by the front-end electronics. In general a pulse with a given 10-90% rise time ( $\tau_{10-90real}$ ) will be observed with a slower value given by:

$\tau_{10-90}^{2} = \tau_{10-90 \text{real}}^{2} + \tau_{\text{min}}^{2}$  where  $\tau_{\text{min}}(\text{ns}) \approx 0.35 \text{ (GHz-ns)} / \text{BW (GHz)}$

If desired, a hardware bandwidth limiter at 20, 200 or 700 MHz can be selected.

| Model Agilent # | Bandwidth into 50 Ω | Minimum Rise Time |

|-----------------|---------------------|-------------------|

| AC210,          | 1GHz                | 0.35 ns           |

| AC240 ≈ U1080A  |                     |                   |

## 3.1.5. Input Voltage and Offset

The input channel provides a fully programmable amplifier with variable input voltage and offset. Full Scale (FS) input voltages are selectable from 50 mV to 5 V in a 1, 2, 5 sequence. Care should be taken to select an input voltage range that will allow the signal to be recorded using as much dynamic range of the digitizer as possible. The variable offset is programmable in the range of  $\pm 2$  V, in the FS ranges 50 to 500 mV, and  $\pm 20$  V, in the FS ranges 1 V to 5 V. The raw 8 bit ADC data values are in the range [-128,+127] with the first and last values reserved for underflow and overflow respectively. The midpoint value, 0, of the range corresponds to the negative of the offset voltage. Thus the Full Scale Range (FSR) goes from

-Offset Voltage - (FS/2) to -Offset Voltage + (FS/2)

Signals going outside of the FSR will be clipped and data values for the clipped portion of a signal should be regarded as erroneous.

## **3.1.6.** Vertical Resolution

The AC Series Analyzers use an ADC system with 8 bits of vertical resolution (256 levels). The dynamic range of the ADC covers the Full Scale (FS) of the Input Voltage setting. For example, if the Input Voltage is set to 500 mV then the ADC resolution is equivalent to 1.95 mV. Analyzers use low noise front-end electronics in order to ensure a good signal to noise ratio. To obtain the best dynamic range from the ADC care should be taken to ensure that the input signal varies over more than 50% of the Input Voltage Full Scale (FS) setting. The highest and lowest levels of the ADC correspond to underflow and overflow conditions.

#### 3.1.7. DC Accuracy

DC voltage accuracy is better than  $\pm 2\%$  ( $\pm 1\%$  typical) of the input voltage full-scale. The differential linearity is better than  $\pm 0.9$  LSB

## 3.2. Trigger

In normal digitizer operation, the trigger signal stops the data acquisition, typically somewhat delayed, depending on the user-specified *delay* value.

When the card is operated as a continuous data analyzer, the trigger signal is routed to the DPU where it is used as an indicator of the time region of interest. However, it does not stop the acquisition.

## 3.2.1. Trigger Source

The trigger source can be a signal applied to either the Input Channel (for internal triggering) or the External Trigger Input.

The modules provide a front panel BNC External Trigger Input. The External Input provides a fully functional trigger circuit with a fixed 50  $\Omega$  termination impedance, as well as selectable level and slope. It has the same BW limiter selections as can be found for the input channel. The user can choose the external trigger Full Scale from the set of values 0.5, 1.0, 2.0 or 5.0 V. A ±5 V limit on trigger signals should be respected, although somewhat higher voltages for short time periods will not damage the unit.

## **3.2.2.** Trigger Coupling

Trigger coupling is used to select the coupling mode applied to the input of the trigger circuitry. Modes available include AC LF Reject, HF Reject, and DC. The AC LF Reject mode couples signals capacitively and removes the input signal's DC component and frequencies below 50 Hz. DC mode allows all signal components to be passed through to the trigger circuit. The HF Reject mode removes signal components above 50 kHz.

#### 3.2.3. Trigger Level

The trigger level specifies the voltage at which the selected trigger source will produce a valid trigger. The trigger level is defined as a set voltage. Using the internal trigger with DC coupling, the level is set with respect to the midpoint voltage ( $V_m$ = – Offset voltage) of the digitizer's vertical scale. Internal trigger level settings must be within

$V_m \pm 0.5$  FS, where FS is the channel or External Full Scale. All trigger circuits have sensitivity levels that must be exceeded in order for reliable triggering to occur. Trigger levels are also adjustable when using AC coupling.

AC Series digitizers will trigger on signals with a peak-peak amplitude > 15% FS from DC to their bandwidth limit.

#### 3.2.4. Trigger Slope

The trigger slope defines the direction of the signal that will be used to initiate the acquisition when it passes through the specified trigger level. Positive slope indicates that the signal is transitioning from a lower voltage to a higher voltage. Negative slope indicates the signal is transitioning from a higher voltage to a lower voltage.

#### **3.2.5.** Window Trigger

The AC Series digitizers implement a Window trigger. Two trigger level thresholds are used to define the desired range. The trigger can then be chosen to occur either when the signal exits or enters the window range. This mode can be thought of as the appropriate OR of two edge triggers of opposite slope.

#### **3.2.6.** HF Trigger

The AC Series digitizers implement an HF trigger that allows triggers to be reliably accepted at rates above  $\sim 1$  GHz. In this mode, triggers occur on every fourth positive edge. The window trigger is not available in this mode.

## 3.2.7. Pre- and Post-Trigger Delay

The pre- and post-trigger counters are only used in normal digitizer mode. When the card is operated as a continuous data analyzer, no acquisition trigger is required. The pre- and post-trigger counters are therefore ignored at this level.

To increase trigger flexibility a pre- or post-trigger delay can be applied to the trigger position.

The amount of pre-trigger delay can be adjusted between 0 and 100% of the acquisition time window (i.e. sampling interval x number of samples), whereas the post-trigger delay can be adjusted between 0 and 200 million samples.

Pre- or post-trigger delays are just different aspects of the same trigger positioning parameter:

- The condition of 100% pre-trigger indicates that all data points are acquired prior to the trigger, i.e. the trigger point is at the **end** of the acquired waveform.

- The condition of 0% pre-trigger (which is identical to a post-trigger of 0) indicates that all data points are acquired immediately after the trigger, i.e. the trigger point is at the **beginning** of the acquired waveform.

- The condition of a non-zero post-trigger delay indicates that the data points are acquired after the trigger occurs, at a time that corresponds to the post-trigger delay, i.e. the trigger point is **before** the acquired waveform.

The digitizer hardware accepts pre- and post-trigger adjustments in increments of 16 samples. By definition post-trigger settings are a positive number and pre-trigger settings are a negative number.

Thus it is only natural that the software drivers provided treat pre- and post-trigger delays as a single parameter in seconds that can vary between *-nbrSamples* \* *samplingInterval* (100% pre-trigger) and *+maxPostTrigSamples* \* *samplingInterval* (max post-trigger of 200M samples). Since the Acqiris software drivers provide very accurate trigger position information upon waveform readout, the accepted resolution of the user-requested pre-/post-trigger delay is much better than 16 samples. For more details, refer to the **Programmer's Reference Manual**.

## 3.2.8. Trigger Status

The front panel includes a tri-color LED indicator to show the status of the trigger for normal digitizer mode. This LED indicator is located near the TRIGGER IN BNC Connector.

When the LED is green it indicates the trigger is armed and waiting for a valid trigger to occur. Red indicates that the trigger has occurred, the acquisition is complete, and the data is waiting to be read out. The user can override the default functions and program the LED color in an application-specific manner.

When the AC Series are used as an analyzer this LED is always green when the acquisition is continuously running.

## 3.3. Sampling Rate

All Acqiris digitizers contain an analog-to-digital conversion (ADC) system that can sample waveforms, in a real time sampling mode, at rates from the maximum allowed rate down to 100 S/s (10 ms per point). The sampling rate can be programmed and is selectable in a 1, 2, 2.5, 4, 5 sequence (i.e. 1 MS/s, 2 MS/s, 2.5 MS/s, 4 MS/s, 5 MS/s, 10 MS/s, etc.). The maximum sampling rate shown above sometimes exploits the possibility of combining channels. The AC210 can sample up to 1 GS/s and the AC240 up to 2 GS/s. The data of all of the active channels is acquired

synchronously; all of the ADC's are acquiring data at the same time, to within a small fraction of the maximum sampling rate.

## 3.4. Data Acquisition - Digitizer Mode

Data from the ADC are stored in on-board acquisition memory. The amount of memory in use for acquisition can be programmed and is selectable from 2 points to 128 Kpoints, the full amount of acquisition memory available.

For technical reasons, a certain memory "overhead" is required for each waveform, reducing the available memory by a small amount. In order to simplify programming, an interface function recommends the best sampling rate and the maximum possible number of data points, taking into account the available memory, the requested time window, the number of segments (in Sequence mode), as well as the required memory overhead.

The Time Base Range defines the time period over which data is being acquired. For example, the AC210 in the digitizer mode has an acquisition memory of just under 128 Kpoints and maximum sampling rate of 1 GS/s. Thus, at the maximum sampling rate, the digitizer can record a signal over a time period of up to 130  $\mu$ s (128 Kpoints \* 1 ns/point). The time base range can be adjusted by varying the amount of acquisition memory or the sampling rate of the digitizer.

## 3.5. Data Processing – Analyzer Mode

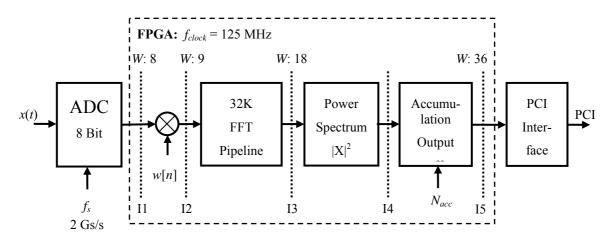

Data from the ADC are continuously streamed through the data demultiplexer (MAC) to the on-board Data Processing Unit. The Data Processing Unit of the AC Series is implemented as a large field-programmable gate array (FPGA) with optional external memory.

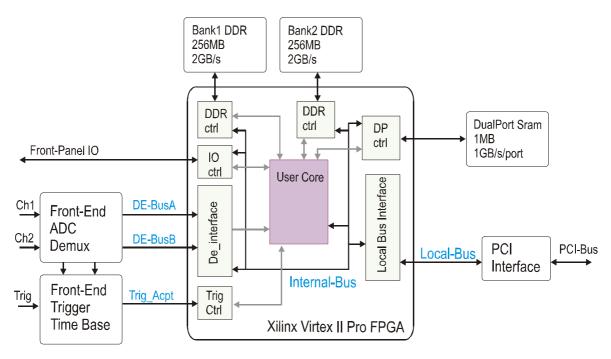

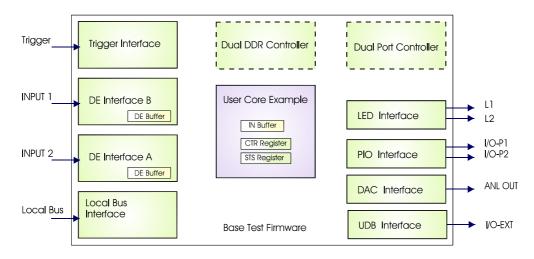

The figure below presents the Data Processing hardware environment and some of the basic blocks used to interface them.

## 3.5.1. Data Processing Unit

The Data Processing Unit is well suited for many data processing schemes. It is implemented as a powerfull FPGA, the Xilinx Virtex II Pro XC2VP70-6FF1517 that provides up to two embedded PowerPCs, 328 18-bit x 18-bit multipliers, and 328 block RAMs.

The main features are summarized in the table below. Please refer to http://www.xilinx.com for the latest information about this device.

| Resources   | Qty   | Description / Comment                                       |

|-------------|-------|-------------------------------------------------------------|

| Logic cells | 66176 | 1 Logic cell has 1x (4 Input LUT + Flip-Flop + Carry Logic) |

| Block RAM   | 328   | Instances of block RAM, 18 kbits each                       |

| Multiplier | 328 | 18-bit x18-bit multipliers                                                                                |

|------------|-----|-----------------------------------------------------------------------------------------------------------|

| DCM        | 8   | Digital clock manager including frequency synthesis and phase shifting features. Frequency up to 420 MHz. |

| BUFG       | 16  | Global Clock Buffer                                                                                       |

| Rocket IO  | 16  | Not connected                                                                                             |

| PowerPC    | 2   | No support from Acqiris                                                                                   |

In addition, the P512MB Memory option can improve the processing capability.

The Analyzer functions are completely dependent on the firmware downloaded into the Data Processing Unit. The application-specific firmware available for the AC2x0 Series is described in chapter 4 *FIRMWARE*.

As an option, a FDK (Firmware Development Kit) for the Acqiris AC2x0 series enables users to develop and integrate user-specific data processing algorithms. The FDK reduces the development effort by providing a set of cores that interface to the underlying hardware resources. Please refer to the FDK Reference Manual for more information.

## 3.5.2. Memory Option

The external DPU memory option consists of:

- 2 banks of 256MB of DDR333 SDRAM with a throughput of up to 2 GB/s per bank.

- 1 MB of dual-port SRAM with a read/write throughput of up to 1 GB/s per port.

Each DDR bank is built around four 512Mbit DDR-SDRAM devices that are organized as 8M x 16bits x 4 banks. Data are synchronously transferred on a 64-bit wide bus on each edge of a 166.67 MHz clock. A DDR Controller that is able to sustain continuous burst reading or writing at a data rate of up to 2 GB/s is provided as part of the FDK.

The Dual Port Memory is built around two 4Mbit Dual Port SRAM organized as 128K x 36 bits. Data are synchronously transferred on a 64-bit wide bus on each port using a clock at up to 166.67 MHz. A Dual Port Controller that is able to sustain continuous simultaneous burst reading and writing at a data rate of up to 1 GB/s is provided as part of the FDK.

## **3.5.3.** Extended Data Processing Controls

The AC Series provides several front-panel connectors for real-time control of the DPU. The function of these connectors and LEDs is user defined through the implemented firmware.

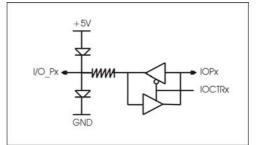

Two front-panel digital I/O MMCX-type connectors (I/O P1 & P2) are dedicated to the direct control of the data processing unit. These signals are 3.3 V compatible CMOS.

Each digital I/O can independently be configured either as an input or as an output. The figure below shows the equivalent schematic of one I/O Px interface.

The series resistor value is 50  $\Omega$ . I/O Px and I/O CTRx signals are connected to the Data Processing Unit.

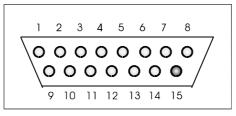

A third MMCX front-panel coaxial connector (ANL Out) is an analog output signal whose voltage is driven by a 16bit on-board serial DAC. This analog signal can be used in simple control systems. The voltage range of that signal is -5V to +5V. The typical settling time (full scale range) is 1µs. A front-panel  $\mu$ DB-15 connector (I/O EXT) provides fourteen bi-directional direct lines to the DPU that can be used as seven differential pairs or as fourteen closely coupled single ended lines. Please note that these lines must use 2.5V signaling logic standards.

$\wedge$

# **CAUTION:** Do not exceed the maximum input voltage rating! The maximum input voltage for µDB-15 Connector is 2.6 V.

The figure below shows the pinout of the µDB-15 connector. Pin 15 is connected to the electrical ground.

The table below shows the pinout allocation of the I/O EXT connector. Each DPxn/DPxp pair refers to two lines routed towards the data processing unit as a differential pair.

| Pin   | Allocation  |

|-------|-------------|

| 1 - 2 | DP6n – DP6p |

| 3 - 4 | DP5p – DP5n |

| 5 - 6 | DP4p – DP4n |

| 7 - 8 | DP0p – DP0n |

| 9-10  | DP3p – DP3n |

| 11-12 | DP2p – DP2n |

| 13-14 | DP1p – DP1n |

| 15    | GND         |

Finally, two LEDs (L1 & L2) provide a visual reference. Each LED is independently driven by the Data Processing Unit and displays one of the four following colors (Black or switched off, Red, Green, or Orange).

## **3.6.** External Clock and Reference

For applications where the user wants to replace the internal clock of the digitizer in order to drive the ADC with an external source, an External Clock or Reference signal input is available. The Clock or Reference signals can be entered into the digitizer via the MMCX CLK IN connector on the front panel.

When using an External Clock, the user must ensure that the input signal has a frequency between 10 MHz and 2 GHz, and a minimum amplitude of at least 1 V, peak to peak, into 50  $\Omega$ . The External Clock allows the digitizer to make a voltage measurement whenever the clock signal passes through a predefined threshold. However, it should be noted that when 2 channels are being used the maximum Sampling Rate is half of the External Clock Frequency in the Continuous mode and in this case the Start/Stop mode is to be preferred. The threshold range is variable and user selectable between  $\pm 2$  V. The signals should not exceed  $\pm 5$  V amplitude.

For applications that require greater timing precision and stability than is obtainable from the internal clock, a 10 MHz Reference signal can be used. The amplitude and threshold conditions, for an External Reference, are the same as for the External Clock. If phase synchronization between several digitizers is required, the reference signal should be applied to all of them.

## **3.7.** Internal Calibration

The software drivers supplied include calibration functions for the timing, gain, and offset settings, which can be executed upon user request. The digitizers are never calibrated in an "automatic" way, i.e. as a side effect of another operation. This ensures that programmers have full control of all calibrations performed through software in order to maintain proper event synchronization within automated test applications.

The AC2x0 includes a high precision voltage source and a 16-bit DAC, used to determine the input voltage and offset calibration.

For accurate time and voltage measurements it is recommended to perform a calibration once the module has attained a stable operating temperature (usually reached with a few minutes after power on). Further calibration should not be necessary unless temperature variations occur. Calibration can usually be performed with signals present at the channel, external, and clock inputs. However, if the calibration is found to be unreliable, as shown by a calibration failure status, it may be necessary to remove such signals.

#### 3.8. External Trigger Output

When the module is ready to be triggered and a valid trigger signal occurs, a trigger output is generated for external use. It is always available on the Front Panel Trigger Out MMCX connector. The pulse ends when the data acquisition for the trigger in question is complete.

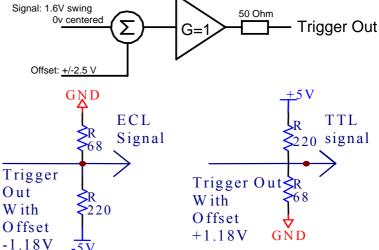

Trigger Output Block diagram:

The output swing is 1.6 V ( $\pm$  0.8 V) when unloaded and 0.8 V when terminated on 50  $\Omega$ . The rise and fall times are 2.5 ns typical. The offset can be adjusted, by software control in the range [-2.5 V, +2.5 V] unloaded, or [-1.25 V, +1.25 V] into 50  $\Omega$ . The maximum output current capability is  $\pm$ 15 mA. As the output is retro-terminated, it is possible to drive a 50  $\Omega$  line unterminated (HiZ) without loss of performance.

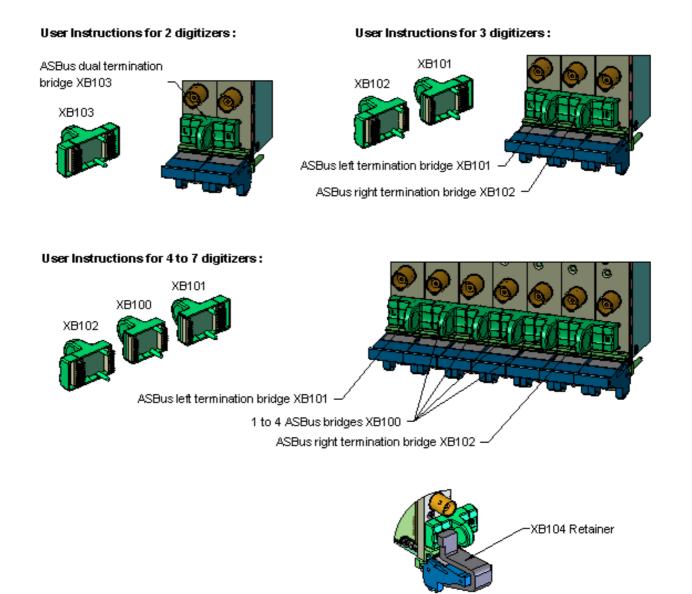

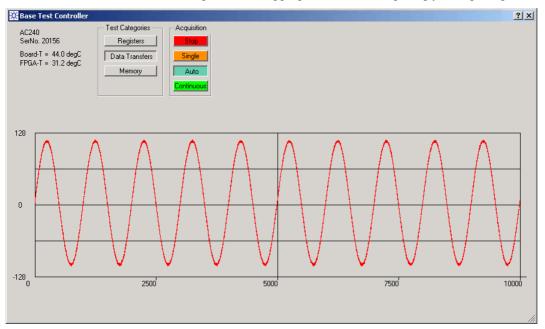

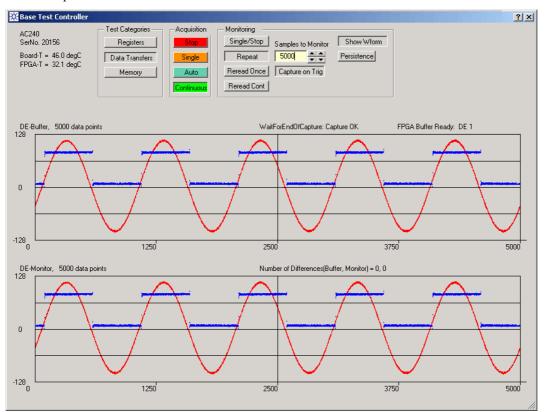

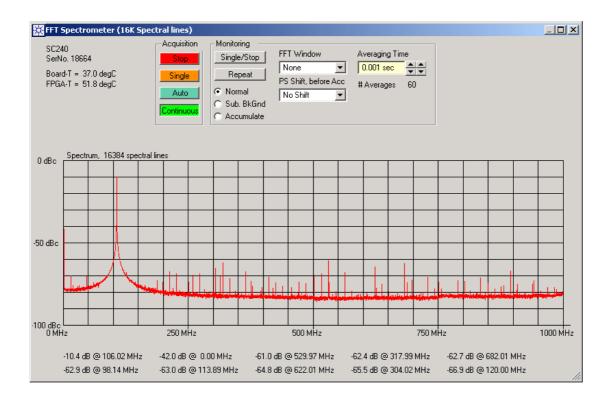

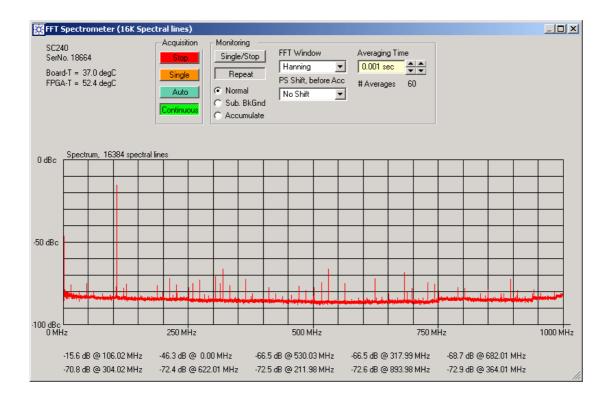

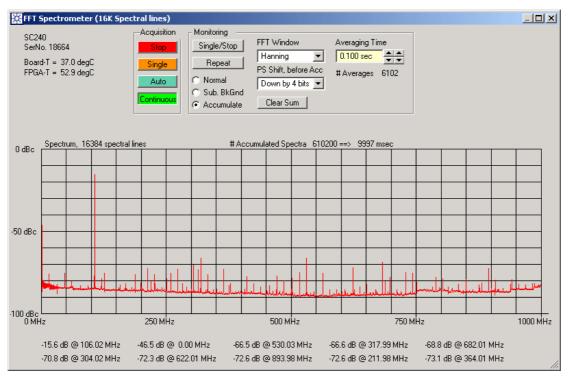

For a TTL compatible signal, set the offset to 1.0 V and the swing at destination will be +0.2 to +1.8 V.